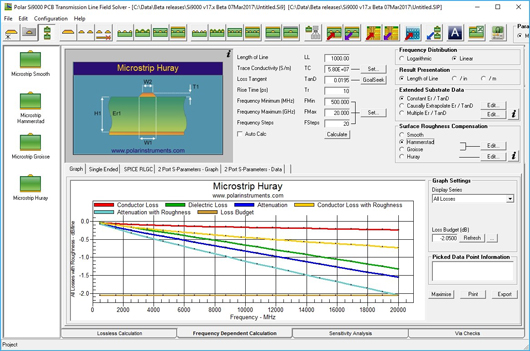

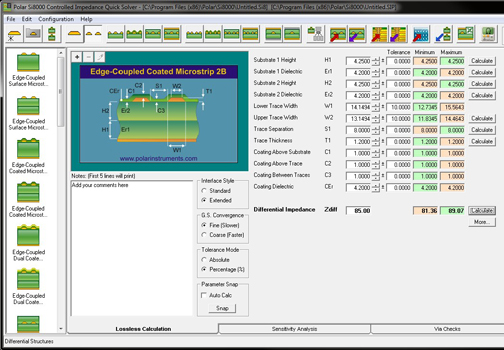

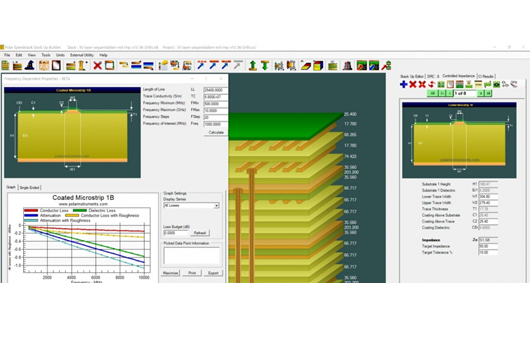

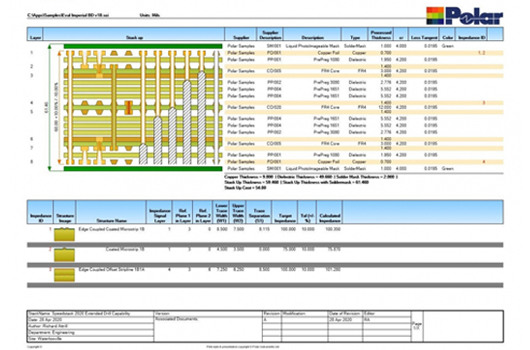

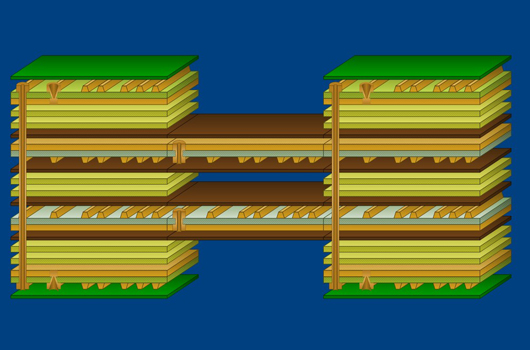

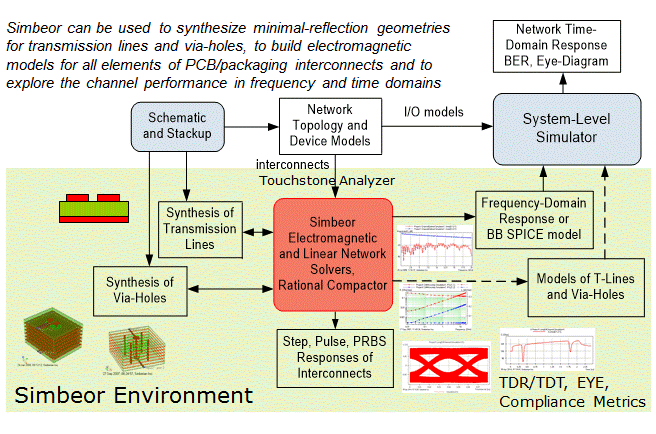

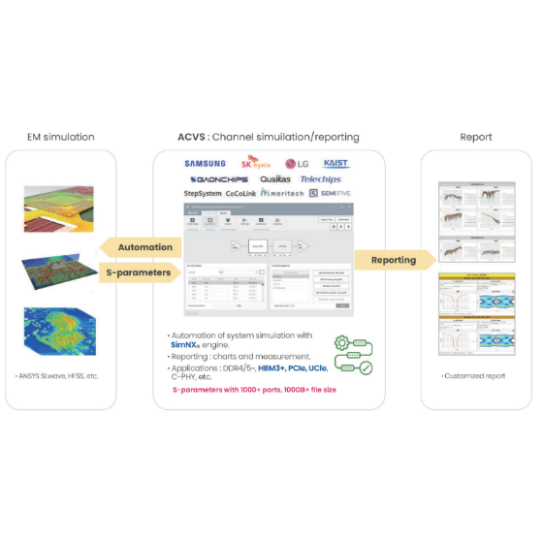

SIMBEOR is a 3D electromagnetic signal integrity tool for simulating and analyzing the entire interconnect link. It offers an industry-first measurement-validated electromagnetic signal integrity software for the physical design of PCB and packaging interconnects for communication links operating at 6-112 Gb/s and beyond. Simbeor is the one-stop solution for all interconnect budget exploration (advanced stackup planning and pre-layout), design verification (post-layout), dielectric and conductor roughness models identification, and macro-modeling tasks. The accuracy of the models is ensured by the use of advanced algorithms for 3D full-wave analysis, benchmarking, and experimental validation. It fits any design flow as a system interconnect budget exploration tool, interconnect verification tool, or a Touchstone model clean-up and macro-modeling tool for automatic S parameter extraction.

Simbeor Solvers and Algorithms:

Simbeor 3DML™ : Full-wave 3D analysis tool for multi-layered geometries:

- Hybrid solver : Method of Lines + Trefftz Finite Elements + Method of Simultaneous Diagonalization (de-embedding)

- Analysis of discontinuities and transmission lines with high-frequency (non-TEM) dispersion and anisotropy (any planar cross-section)

- Simbeor 3DTF™ : First full-wave 3D analysis tool based on Trefftz Finite Elements (aka Ultra-Weak Discontinuous Galerkin's Wave Elements)

Simbeor SFS™ : Unique quasi-static field solver for large t-line cross-sections (any planar cross-section):

- MoM : Supports all dispersive isotropic material and conductor roughness models

- Linear Network solvers : Unique port-based circuit analysis with 7 solvers for frequency and time domain analyses of multiport networks based on Y or S-parameters (with sparse solvers for extremely large multiport networks), capabilities to extract GMS-parameters, test fixture S-parameters and de-embed test fixture

- Rational Compactor™ : Converts discrete S-parameter models into frequency-continuous rational macro-models for consistent frequency and time domain analyses

Simbeor : Tools and Interfaces:

Board Analyzer™ : Post-layout decompositional electromagnetic analysis

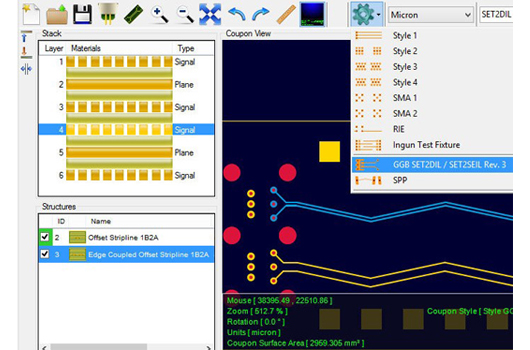

Transmission Line Wizard - Fast synthesis of any single-ended and differential line geometries (strip, microstrip, CPW, CBCPW)

Via Analyzer™ : Fast synthesis of via-holes and launches geometry

Touchstone Analyzer™ : S-parameters plotting, quality assurance, and rational macro-modeling

Geometry Editor : Pre and Post-layout analyses of multi-layered circuits

Linear Network Editor : Draw or edit multiport networks (link path models)

SiTune™ : Material models, geometry and linear network optimization

Board Geometry Translators : ODB++, HyperLynx hyp-file, Allegro brd/mcm, PADS ASCII

Violation Browser™ : Violation viewer for EMSAT rule checker

Eye Analyzer™ : Computation of eye diagram metrics and comparison of eye diagrams

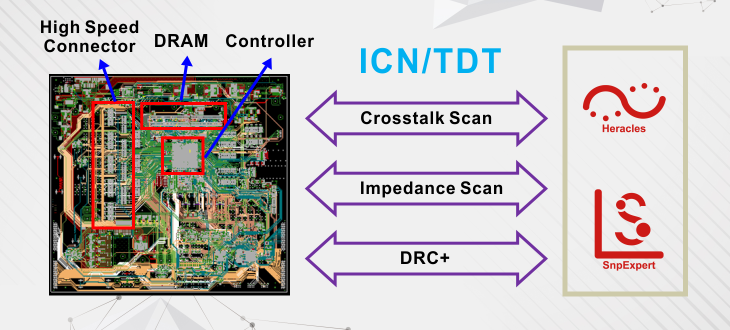

ICN Analyzer™ : Computation of Integrated Crosstalk Noise and a quick comparison with compliance mask

Interactive Graphs : Plot transmission line modal and RLGC(f) parameters, S-parameters, 10G and 25G compliance metrics, TDR/TDT, eye diagram

Batch Mode - Run analysis in batch mode for design automation

Download SIMBEOR Brochure

Applicable only in Greater China, India, Vietnam, Malaysia, Thailand, and Singapore.