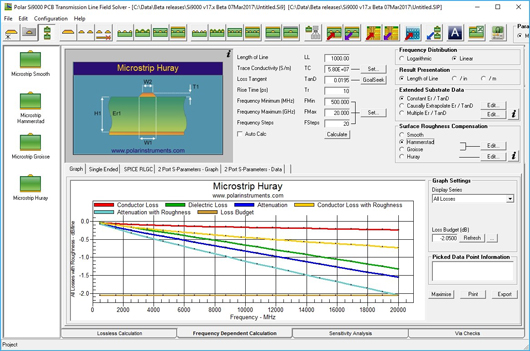

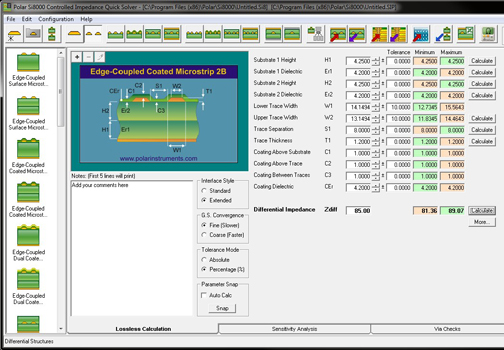

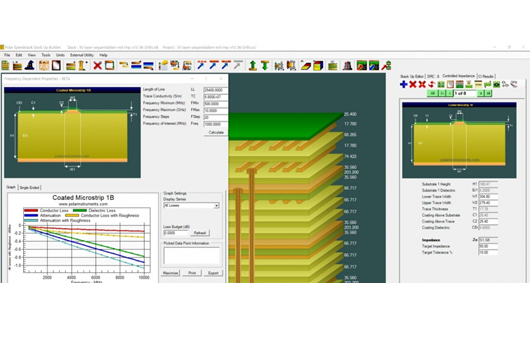

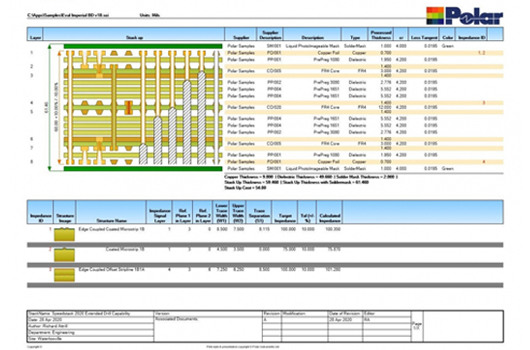

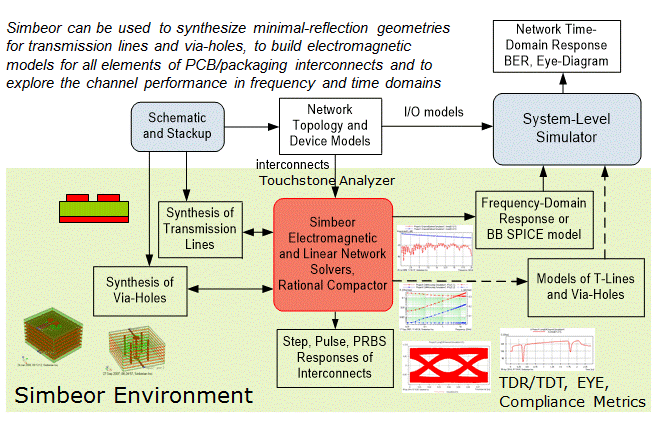

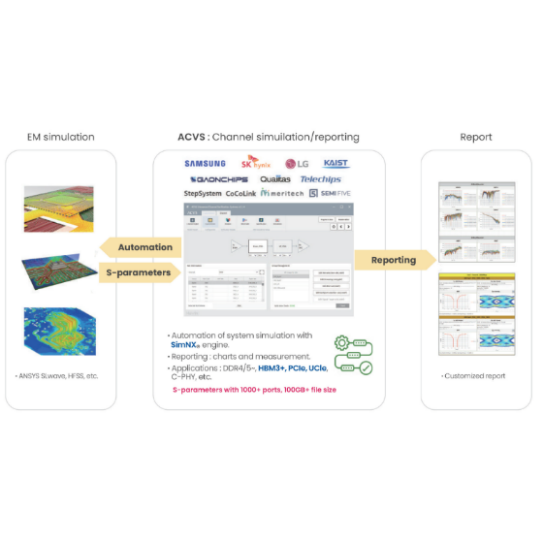

SIMBEOR是3D電磁信號完整性工具,用於模擬和分析整個互連鏈路。 它提供了業界首個經過測量驗證的電磁信號完整性軟件,用於PCB和封裝互連的物理設計,以6-112 Gb / s或更高的速率運行通信鏈路。 Simbeor是一站式解決方案,可用於所有互連預算探索(高級堆疊規劃和預佈局),設計驗證(後佈局),電介質和導體粗糙度模型識別以及marco建模任務。 通過使用用於3D全波分析,基準測試和實驗驗證的高級算法,可以確保模型的準確性。 它適合作為系統互連預算探索工具,互連驗證工具或用於自動S參數提取的Touchstone模型清理和宏建模工具的任何設計流程。

Simbeor求解器和演算法:

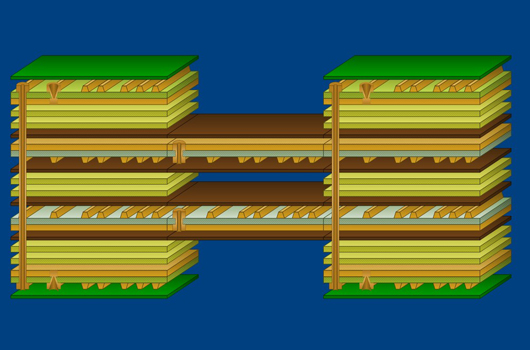

Simbeor 3DML™:用於多層幾何的全波3D分析工具:

- 混合求解器:線法+ Trefftz有限元+同時對角線化(去嵌入)方法

- 分析具有高頻(非TEM)色散和各向異性(任何平面橫截面)的不連續和傳輸線

- Simbeor 3DTF™:第一個基於Trefftz有限元(又名超弱非連續不連續伽勒金氏波元)的全波3D分析工具

Simbeor SFS™:獨特的準靜態場求解器,適用於較大的t線橫截面(任何平面橫截面):

- MoM:支持所有色散各向同性材料和導體粗糙度模型

- 線性網絡求解器:獨特的基於端口的電路分析,帶有7個求解器,用於基於Y或S參數的多端口網絡的頻域和時域分析(具有用於大型多端口網絡的稀疏求解器),提取GMS參數的能力,測試夾具 S參數和去嵌入測試夾具

- Rational Compactor™:將離散的S參數模型轉換為頻率連續的理性macro模型,以進行一致的頻域和時域分析

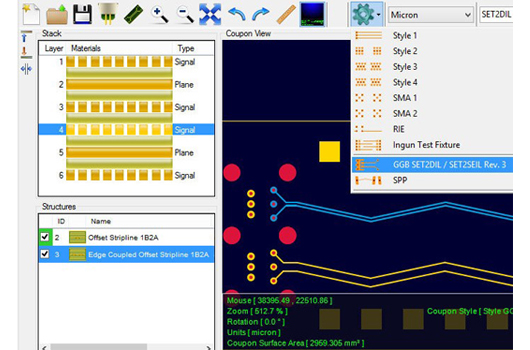

Simbeor:工具和界面:

Board Analyzer™:佈局後分解電磁分析

傳輸線嚮導- 快速合成任何單端和差分線的幾何形狀(帶,微帶,CPW,CBCPW)

Via Analyzer™:快速合成通孔並發射幾何圖形

Touchstone Analyzer™:S參數繪圖,質量保證和合理的macro建模

幾何編輯器:多層電路的佈局前和佈局後分析

線性網絡編輯器:繪製或編輯多端口網絡(鏈接路徑模型)

SiTune™:材料模型,幾何形狀和線性網絡優化

電路板幾何翻譯器:ODB ++,HyperLynx hyp文件,Allegro brd / mcm,PADS ASCII

Violation Browser™:EMSAT規則檢查器的違規查看器

Eye Analyzer™:眼圖指標的計算和眼圖的比較

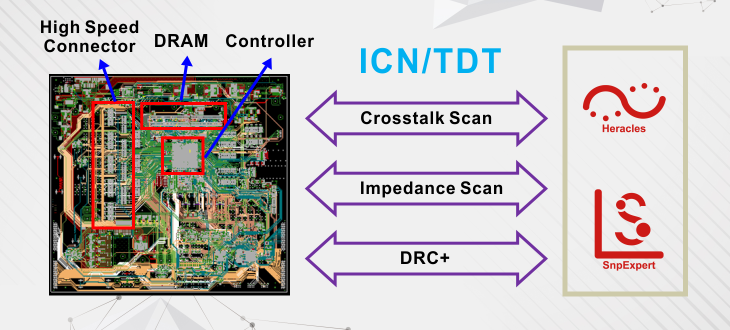

ICN Analyzer™:集成串擾噪聲的計算以及與法規遵從性掩模的快速比較

交互式圖形:繪製傳輸線模態和RLGC(f)參數,S參數,10G和25G符合性指標,TDR / TDT,眼圖批處理模式-以批處理模式運行分析以實現設計自動化

下載SIMBEOR手冊

僅適用於大中華地區,印度,越南,馬來西亞,泰國和新加坡。