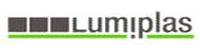

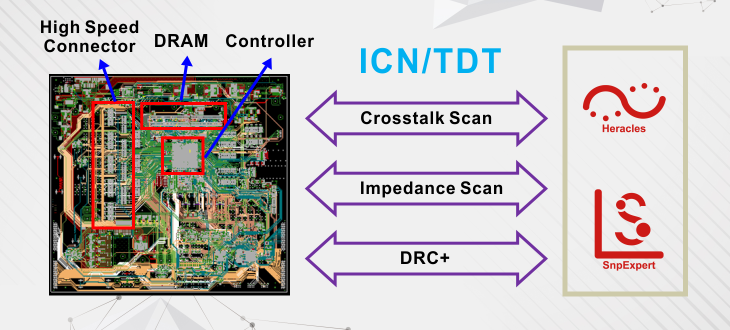

高速通信鏈路設計越向越有挑戰性。半導體和集成電路技術的快速發展加上不斷增加的數據率,增加了挑戰.Xpeedic高速SI解決方案提供一個快速和準確的方法模型和模擬不連續 著路徑和優化信道性能。

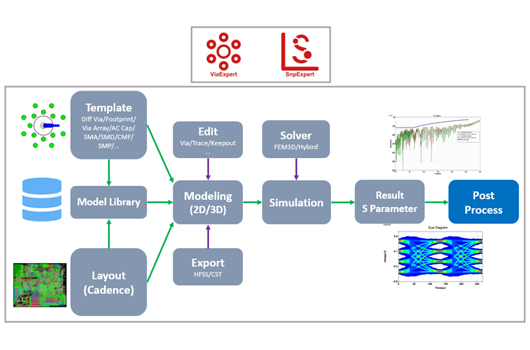

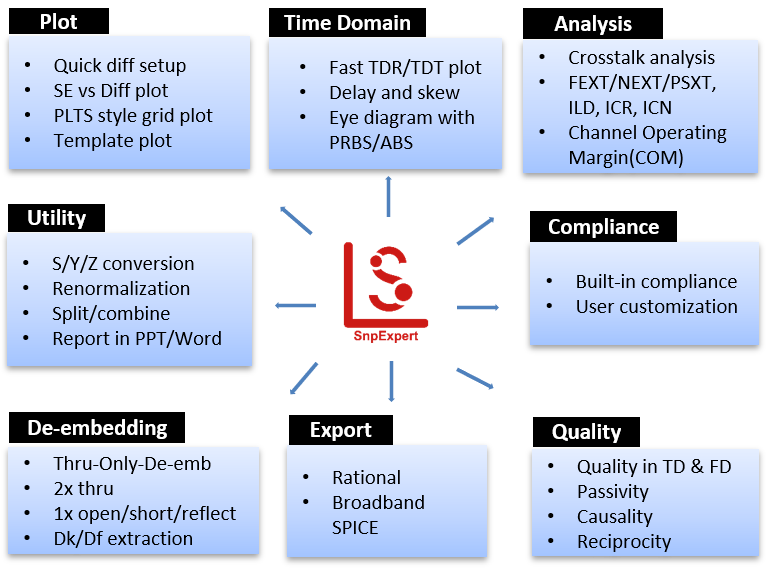

SnPExpert - SnPExpert提供了一種快速的方法來解釋被動接收點的電特性,不僅可以在頻域系統查看S參數,還可以在時域檢查(TDR)。

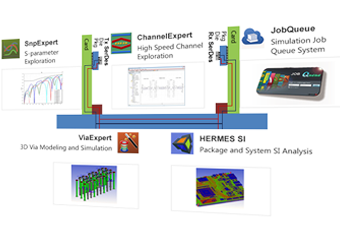

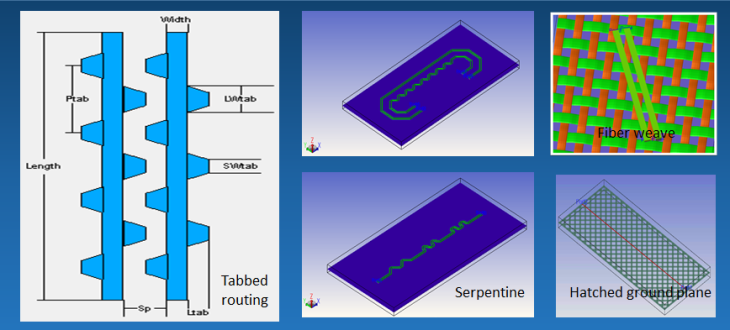

ChannelExpert - ChannelExpert提供了一種快速和準確的方法來解決因為信號完整性問題而引起的級聯網絡的參數塊和TML模型。它的頻域級聯技術和2D-RLCG全波傳輸線解計算器 允許快速和準確的信道仿真。

ViaExpert - ViaExpert模塊提供了一個快速,準確的方法來模擬佈線前和佈線後的場景。內置連接器封裝,對於一個給定的疊層,通過模型與數據庫允許用戶快速組裝連接器封裝,突破區域 跟踪。