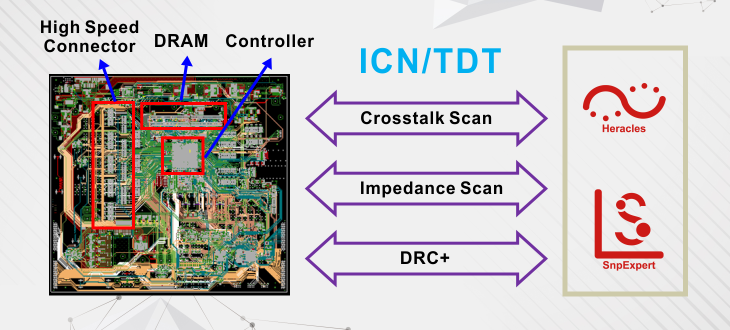

High Speed communication link designs are becoming ever more challenging. The fast pace development of semiconductor and IC technology combined with the ever increasing data rates have added to the challenge. Xpeedic’s High Speed SI solutions provide a fast and accurate way to model and simulate the discontinuities along the path and optimize channel performance.

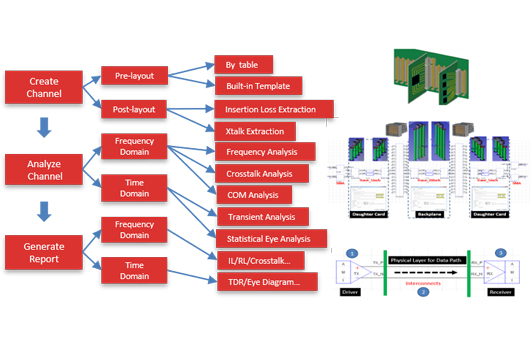

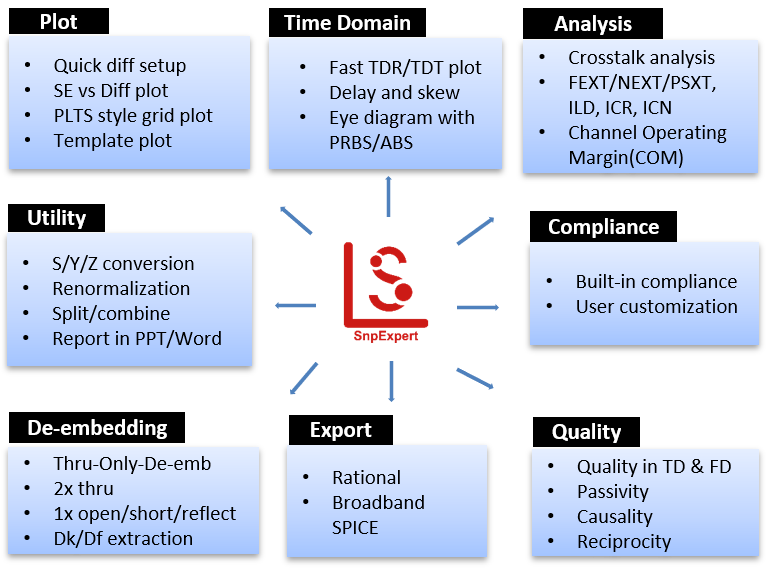

SnPExpert – SnpExpert provides a quick way to understand the electrical characteristics of the passive interconnectors in a system by not only viewing the S-parameter in frequency domain but also examining them in time domain (TDR).

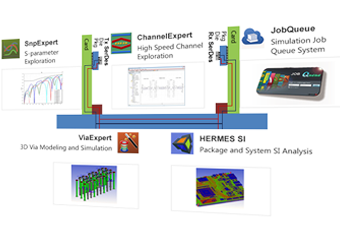

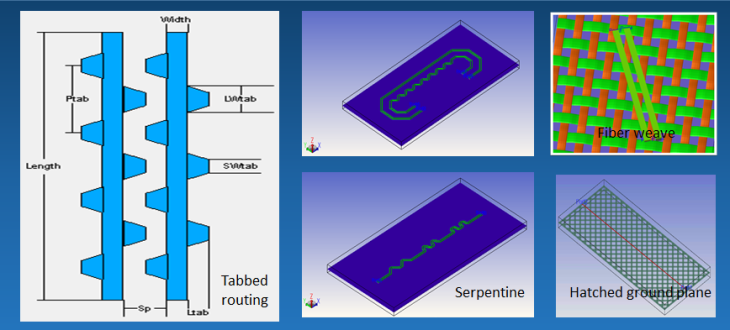

ChannelExpert – ChannelExpert provides a fast and accurate way to address the signal integrity issues arising from cascaded network of S-parameter blocks and TML models. It’s frequency domain cascading technology and 2D-RLCG full wave transmission line solver enables quick and accurate channel simulation.

ViaExpert – ViaExpert provides a fast and accurate way to simulate via structures for both pre-layout and post-layout scenarios. The built-in connector footprint database allow users to quickly assemble the via model with connector footprint, breakout region trace, for a given stackup.